- I2C是由双向串行时钟线SCL和双向串行数据线SDA两条数据线组成。

- I2C总线在传输数据是速率可达100kbps,最高可达400kbps。

- I2C总线上允许接入的设备数量主要决定于总线上的电容量,一般设定为400pF以下。

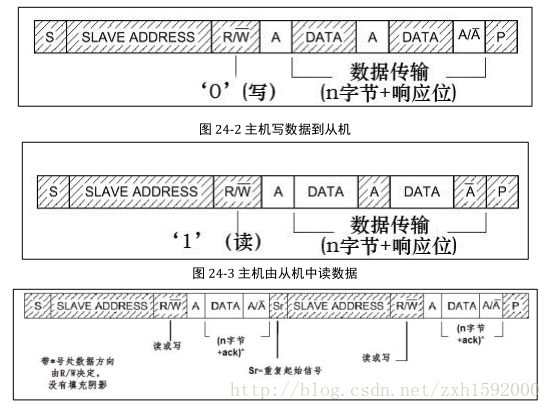

- 总线上传输数据一般由主机发送启动信号和时钟信号,开始传输。一般向主机发出一个地址(7bit),一个读写位(1bit)和一个ACK(1bit)。

- 在I2C上,从机都会装有被控器,被控器每接收一个byte都要在数据线上给主控机发送一个ACK表示完成一个控制功能。在多重主控中存在仲裁过程。仲裁指多个主控器试图同时控制总线,I2C总线只允许其中一个主控器继续占用总线,并保证在整个过程中总线上的数据不会丢失或出错。

- I2C总线上的时钟信号是主控器产生,每个主控器在占用总线传送数据期间都有自己的时钟。SDA数据传输在SCL处于高电平是有效。各主控器向总线上输出不同的时钟频率时,只有通过仲裁过程,才能使总线上有一个统一的时钟信号。

- I2C总线控制中,时钟线将由时钟低电平周期最长的主控器保持为低电平状态,而其他时钟低电平周期较短的主控器将进入时钟高电平等待状态。时钟线高电平周期由时钟信号高电平周期最短的主控器决定。

- ACK是在传输8位后,接收机在第9个SCL内将SDA拉低。以下三种情况没有ACK信号:(1)当从机不能响应从机地址时,这时,主机发出一个P信号终止传输或者重新发出一个S信号开始新的传输。(2)如果从机接收器在传输过程中不能接收更多的数据时,它不会发出ACK信号。(3)主机接收器在接收到最后一个字节后,也不会发出ACK信号。于是,从机发送器释放SDA线,以允许主机发出P信号结束传输。

I2C时序:

需要注意的是:

1,SCL一直由Master控制,SDA依照数据传送的方向,读数据时由Slave控制SDA,写数据时由Master控制SDA。当8位数据传送完毕之后,应答位或者否应答位的SDA控制权与数据位传送时相反。

2,开始位“Start”和停止位“Stop”,只能由Master来发出。

3,地址的8位传送完毕后,成功配置地址的Slave设备必须发送“ACK”。否则否则一定时间之后Master视为超时,将放弃数据传送,发送“Stop”。

4,当写数据的时候,Master每发送完8个数据位,Slave设备如果还有空间接受下一个字节应该回答“ACK”,Slave设备如果没有空间接受更多的字节应该回答“NACK”,Master当收到“NACK”或者一定时间之后没收到任何数据将视为超时,此时Master放弃数据传送,发送“Stop”。

5,当读数据的时候,Slave设备每发送完8个数据位,如果Master希望继续读下一个字节,Master应该回答“ACK”以提示Slave准备下一个数据,如果Master不希望读取更多字节,Master应该回答“NACK”以提示Slave设备准备接收Stop信号。

6,当Master速度过快Slave端来不及处理时,Slave设备可以拉低SCL不放(SCL=0将发生“线与”)以阻止Master发送更多的数据。此时Master将视情况减慢或结束数据传送。